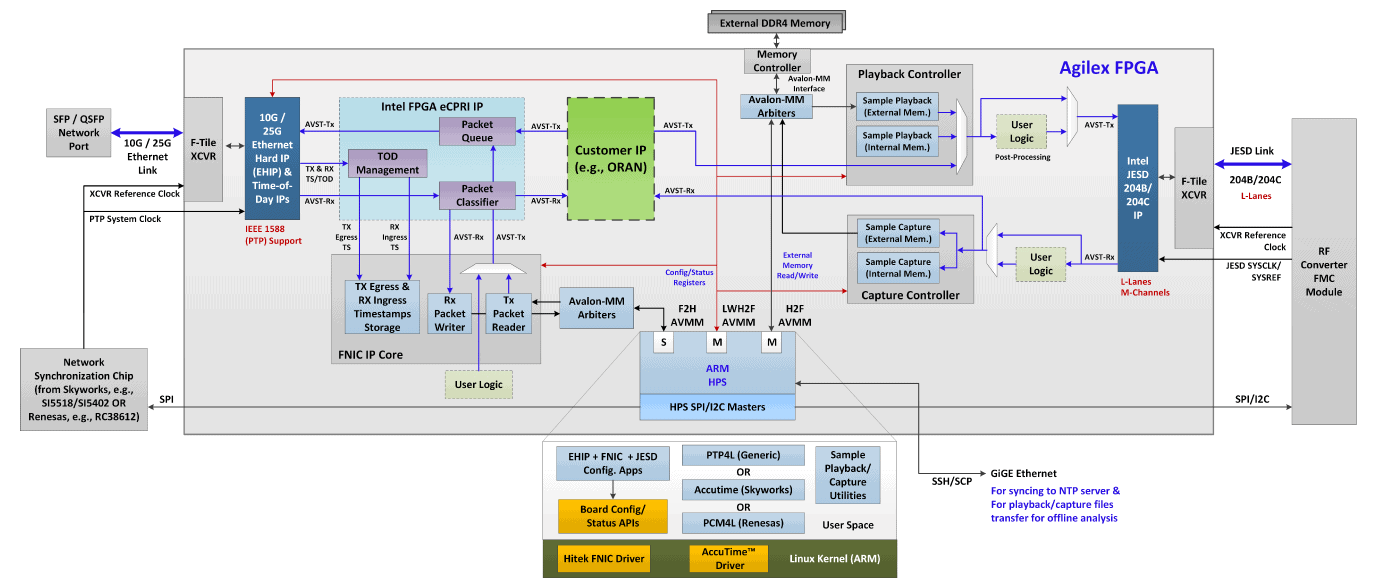

The Agilex eSOM7 5G/Wireless development platform provides a quick evaluation and prototyping platform for 5G ORAN and wireless solutions based on the Intel’s latest high performance 10nm Agilex F-Series FPGAs. The development platform consists of two modules, an Agilex 7 F-Series FPGA based eSOM7 (embedded System On Module) board with two 400-pin high speed mezzanine connectors and a carrier board which implements breakout of the FPGA serdes and I/Os. The carrier module provides a VITA57.4 FMC+ connector with level translation and control logic to interface with ADI RF transceiver evaluation boards.